|

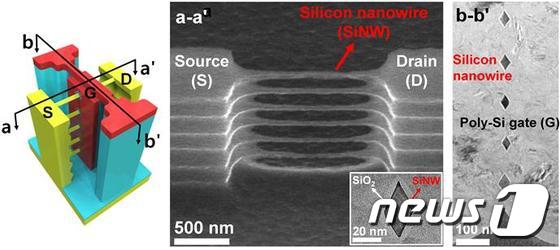

| 서로 다른 방향에서 단면을 관찰한 주사 전자 현미경 사진 및 투과 전자 현미경 사진.© News1 |

한국과학기술원(KAIST)는 23일 전기 및 전자공학부 이병현 연구원과 나노종합기술원 강민호 박사가 실리콘 기반의 5단 수직 적층 반도체 트랜지스터와 이를 이용한 비휘발성 메모리 개발에 성공했다고 밝혔다.연구팀은 전면-게이트 실리콘 나노선을 수직 5단으로 쌓아 문제를 해결했다. 개발된 반도체 트랜지스터는 단일 나노선 기반의 트랜지스터보다 5배의 향상된 성능을 보였다.

|

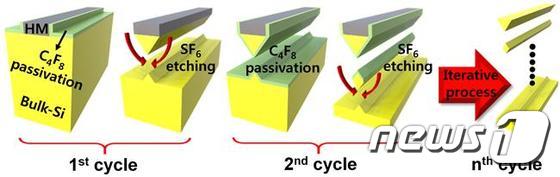

| ‘일괄 플라즈마 건식 식각 공정 과정’의 모식도.© News1 |

특히 나노선 수직 적층은 개발된 '일괄 플라즈마 건식 식각 공정' 방식의 연속 작용을 통해 확보한 결과물이란 분석이다.이 공정은 고분자 중합체를 이용, 패턴이 형성될 영역에 미리 보호막을 친 뒤 등방성 건식 식각을 통해 나노선 구조를 형성하는 기술이다.

연구팀은 "건식 식각 공정 기술이 기존 방법보다 간단하고 안정적으로 수직 적층 실리콘나노선 구조 제작을 가능하게 함으로써 고성능 트랜지스터 개발에 응용 가능할 것"이라고 밝혔다.

또 "관련 연구가 이전부터 진행됐지만 더 간단한 공정기술을 이용, 가장 많은 나노선 채널의 적층에 성공했다"며 "앞으로 비용절감 및 제작 시간 단축 등에 크게 기여할 것으로 예상된다"고 말했다.

|

| KAIST 전기 및 전자공학부 이병현 연구원.© News1 |

etouch84@news1.kr

!['애틋' 최준희, 故 '맘' 최진실·'대드' 조성민 모습 공개…절반씩 닮았네 [N샷]](https://image.news1.kr/system/photos/2024/4/27/6620308/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)

![뉴진스 하니, 몽환·러블리 오가는 매력...깜찍 처피뱅 [N화보]](https://image.news1.kr/system/photos/2024/4/26/6618937/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)

![이민정, 이탈리아서 뽐낸 우아한 분위기...미모에 각선미까지 [N화보]](https://image.news1.kr/system/photos/2024/4/25/6616416/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)