|

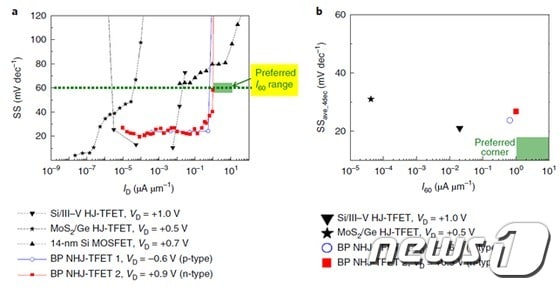

| 카이스트 연구팀이 개발한 흑린 자연이종접합 터널 트랜지스터(BP NHJ-TFET)와 이전까지 개발되었던 트랜지스터의 성능비교. (KAIST 제공) © 뉴스1 |

KAIST(총장 신성철)는 물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터 대비 작동전력 소모량은 10배 이상, 대기전력 소모량은 1만 배 가까이 적은 저전력 고속 트랜지스터를 개발했다고 20일 밝혔다.연구팀은 2차원 물질인 흑린의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 두 물질의 접합이 아닌 단일 물질의 두께 차이에 의한 이종접합 터널을 제작하는 데 성공했다.

이러한 단일 물질의 이종접합을 터널 트랜지스터에 활용하면 서로 다른 물질로 제작한 이종접합 트랜지스터에서 발생했던 격자 불균형, 결함, 계면 산화 등의 문제를 해결할 수 있어 고성능 터널 트랜지스터의 개발이 가능하다.

2차원 물질 기반의 저전력 트랜지스터가 기존의 금속 산화물 반도체 전계효과 트랜지스터의 전력 소모 문제를 해결하고, 궁극적으로 기존 트랜지스터를 대체하고 미래의 저전력 대체 트랜지스터가 될 수 있음을 의미한다.

무어 법칙에 따른 트랜지스터 소형화 및 집적도 증가는 현대의 정보화 기술을 가능하게 했지만 최근 트랜지스터의 소형화가 양자역학적 한계에 다다르면서 전력 소모가 급격히 증가해 무어 법칙에 따라 트랜지스터 소형화가 진행되지 못하는 상황이다. 최근에는 자율주행차, 사물인터넷 등의 등장으로 많은 양의 데이터를 저전력, 고속으로 처리할 수 있는 비메모리 반도체의 기술 발달이 시급히 요구되고 있다.

|

| 조성재 교수(오른쪽)와 김성호 연구원. (KAIST 제공)© 뉴스1 |

조성재 교수는 “기존의 어떤 트랜지스터보다 저전력, 고속으로 작동해 실리콘 기반의 CMOS 트랜지스터를 대체할 수 있는 저전력 소자의 필요충분조건을 최초로 만족시켰다”며 “대한민국 비메모리 산업뿐 아니라 세계적으로 기초 반도체 물리학 및 산업 응용에 큰 의의를 지닌다”고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

KAIST 김성호 연구원이 제1 저자로 참여한 이번 연구 성과는 국제 학술지 ‘네이처 나노테크놀로지'(Nature Nanotechnology) 온라인 판에 지난 1월 27일 게재됐다.

memory444444@nate.com

![최준희, 母 최진실 쏙 빼닮은 물오른 미모…점점 더 예뻐지네 [N샷]](https://image.news1.kr/system/photos/2024/4/20/6607924/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)

![뉴진스 다니엘, 소파 위 도발 눈빛...탄탄 복근까지 [N화보]](https://image.news1.kr/system/photos/2024/4/16/6599923/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)